项目简介

本项目设计开发了一种三维集成阻变存储器的制备-编程解决方案。在不增加工艺复杂度的情况下,设计制备了一种适合于三维集成,并具有自整流特性的阻变存储器。此外,本项目通过改进三维垂直阻变存储器阵列的编程和读取操作方法,减少了误编程概率,能实现更精确的读操作。

应用范围

随着移动设备、物联网、人工智能等领域的快速发展,对低功耗、高容量的存内计算单元的需求不断增长,该发明具有广阔的应用前景。该项目相关技术展示出了存储介质的高存储密度,低制备成本,高编程精度等优点,有望广泛应用于边缘端智能芯片领域,实现高能效高面效的存内计算。在图像识别方面,相关技术可用于开发高性能的机器视觉芯片,实现对图像、视频等视觉信息的快速捕捉和分析,应用于无人驾驶、智能监控、机器人视觉等场景。在语音处理方面,相关技术可用于开发高集成度的语音识别/合成芯片,为智能家居、可穿戴设备等提供自然语言交互功能,大幅提升用户体验。

项目阶段

本项目目前处于研发阶段,已完成方案设计与验证。在交叉阵列结构的自整流阻变存储器制备,三维垂直阻变存储器阵列及其操作方案方面取得了阶段性进展。相关成果已发表在IEEE ASICON等国际会议上。在目前正在积极寻找厂家合作进行商业化应用。

知识产权

相关研究成果已获得2项国家发明专利授权。

1、专利号CN201110452945.3

具有交叉阵列结构的自整流阻变存储器及制备方法

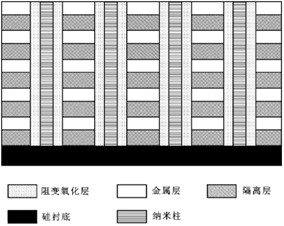

本发明公开了一种具有交叉阵列结构的自整流阻变存储器及制备方法,涉及半导体集成电路及其制造技术领域,所述存储器包括:硅衬底,在所述硅衬底上设有至少一个与其垂直的纳米柱,绕所述纳米柱的侧壁一周设有阻变氧化层,绕所述阻变氧化层的外侧壁一周设有从下至上间隔设置的隔离层和金属层,所述纳米柱的材料为重掺杂硅。本发明通过按照一定的结构设置,实现了在不增加工艺复杂度的情况下,提供了一种适合于三维集成,并具有自整流特性的存储器。

2、专利号:CN202010369772.8

三维垂直阻变存储器阵列及其操作方法、装置、设备及介质

一种三维垂直阻变存储器阵列及其操作方法、装置、设备及介质。该操作方法包括:选中三维垂直阻变存储器阵列中的特定阻变存储器作为选中单元进行编程操作。上述编程操作包括:在选中单元所在的字线、位线和选择线分别对应施加电压Vdd、0和Von1;在与选中单元对应不同选择线的第一非选中单元所在的选择线施加零电压;以及在与选中单元对应同一选择线的第二非选中单元对应的字线和位线中,除去选中单元所在字线和位线之外,其余字线施加电压V1,其余位线施加电压V2;其中,电压V1、V2满足:使得所有第二非选中单元的电压降均小于Vdd/2。在编程操作时克服了由于阻变存储器自身压降及对应的编程电压的涨落而导致的误编程操作。

合作方式

合作开发、技术转让、技术许可。

联系方式

邮箱:kjkfb@pku.edu.cn